一、SOC芯片是什么?

SOC的定义多种多样,由于其内涵丰富、应用范围广,很难给出准确定义。一般说来,SOC系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。

从狭义角度讲,它是信息系统核心的芯片集成,是将系统关键部件集成在一块芯片上;

从广义角度讲, SOC是一个微小型系统,如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。国内外学术界一般倾向将SOC定义为将微处理器、模拟IP(Intellectual Property)核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。

1、SOC的芯片的构成

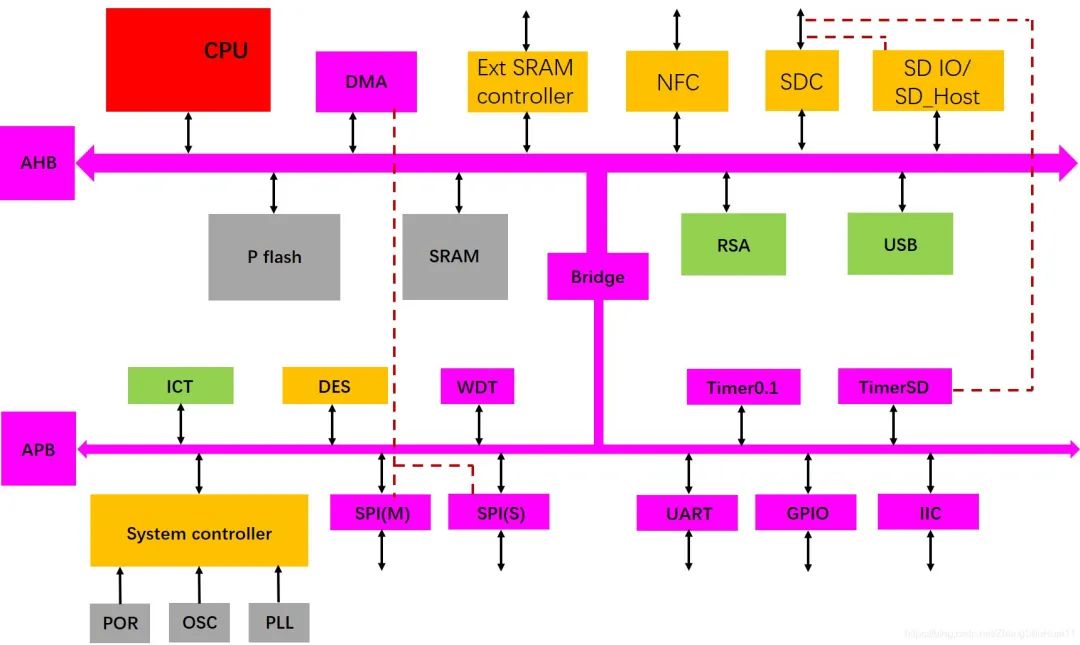

是系统级芯片控制逻辑模块、微处理器/微控制器CPU 内核模块、数字信号处理器DSP模块、嵌入的存储器模块、和外部进行通讯的接口模块、含有ADC /DAC 的模拟前端模块、电源提供和功耗管理模块,对于一个无线SOC还有射频前端模块、用户定义逻辑(它可以由FPGA 或ASIC实现)以及微电子机械模块,更重要的是一个SOC芯片内嵌有基本软件(RDOS或COS以及其他应用软件)模块或可载入的用户软件等。

2、SOC的形成过程

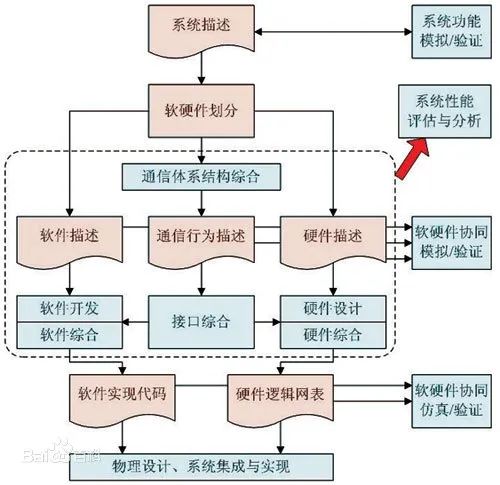

(1)基于单片集成系统的软硬件协同设计和验证;

(2)再利用逻辑面积技术使用和产能占有比例有效提高即开发和研究IP核生成及复用技术,特别是大容量的存储模块嵌入的重复应用等;IP核复用技术在SOC芯片设计中被广泛采用。先进工艺条件下,SoC系统级芯片设计规模越来越大,芯片上所集成的IP种类和数量也随之暴增。IP数据如何高效管理和追踪变得尤为重要。

(3) 超深亚微米(VDSM) 、纳米集成电路的设计理论和技术。

3、SOC设计的关键技术

SOC关键技术主要包括总线架构技术、IP核可复用技术、软硬件协同设计技术、SOC验证技术、可测性设计技术、低功耗设计技术、超深亚微米电路实现技术,并且包含做嵌入式软件移植、开发研究,是一门跨学科的新兴研究领域。

二、SOC芯片的优缺点

优点

1. 芯片尺寸小。受益于MOS技术,SOC片可实现功能增加的同时,芯片尺寸大大减小。

2. 低功耗。SOC的低功耗性能,可提高电子设备 (如手机)的整体使用时间

3. 可再编程。开发人员可对SOC芯片再编程,重复使用IP。

4. 可靠性强。SOC芯片提高电路安全性并降低设计复杂性;

5. 成本效益高。SOC相比其他电子器件,具有更少的物理组件和可再次设计;

6. 更快的运行速度;

缺点

1. 生产周期长。SOC芯片从设计到制造出货整个过程在6个月到1年左右;

2. 设计验证时间长。SOC芯片的设计验证环节约占总周期的70%;

3. IP核的授权和兼容情况大大影响产品上市时间;

4. 制造成本指数型增长;

5. 对于小批量的产品,SOC不是最好的选择;

三、SOC芯片设计流程

1.功能设计阶段

设计人员产品的应用场合,设定一些诸如功能、操作速度、接口规格、环境温度及消耗功率等规格,以做为将来电路设计时的依据。更可进一步规划软件模块及硬件模块该如何划分,哪些功能该整合于SOC 内,哪些功能可以设计在电路板上。

2.设计描述和行为级验证

功能设计完成后,可以依据功能将SOC 划分为若干功能模块,并决定实现这些功能将要使用的IP 核。此阶段间接影响了SOC 内部的架构及各模块间互动的讯号,及未来产品的可靠性。决定模块之后,可以用VHDL 或Verilog 等硬件描述语言实现各模块的设计。接着,利用VHDL 或Verilog 的电路仿真器,对设计进行功能验证(functionsimulation,或行为验证 behavioral simulation)。注意,这种功能仿真没有考虑电路实际的延迟,但无法获得精确的结果。

3.逻辑综合

确定设计描述正确后,可以使用逻辑综合工具(synthesizer)进行综合。综合过程中,需要选择适当的逻辑器件库(logic cell library),作为合成逻辑电路时的参考依据。硬件语言设计描述文件的编写风格是决定综合工具执行效率的一个重要因素。事实上,综合工具支持的HDL 语法均是有限的,一些过于抽象的语法只适于做为系统评估时的仿真模型,而不能被综合工具接受。逻辑综合得到门级网表。

4.门级验证(Gate-Level Netlist Verification)

门级功能验证是寄存器传输级验证。主要的工作是要确认经综合后的电路是否符合功能需求,该工作一般利用门电路级验证工具完成。注意,此阶段仿真需要考虑门电路的延迟。

5.布局和布线

布局指将设计好的功能模块合理地安排在芯片上,规划好它们的位置。布线则指完成各模块之间互连的连线。注意,各模块之间的连线通常比较长,因此,产生的延迟会严重影响SOC的性能,尤其在0.25 微米制程以上,这种现象更为显著。

集成电路的发展已有40年的历史,它一直遵循摩尔所指示的规律推进,现已进入深亚微米阶段。由于信息市场的需求和微电子自身的发展,引发了以微细加工(集成电路特征尺寸不断缩小)为主要特征的多种工艺集成技术和面向应用的系统级芯片的发展。随着半导体产业进入超深亚微米乃至纳米加工时代,在单一集成电路芯片上就可以实现一个复杂的电子系统,诸如手机芯片、数字电视芯片、DVD 芯片等。

在未来几年内,上亿个晶体管、几千万个逻辑门都可望在单一芯片上实现。SOC(System - on - Chip)设计技术始于20世纪90年代中期,随着半导体工艺技术的发展,IC设计者能够将愈来愈复杂的功能集成到单硅片上,SOC正是在集成电路( IC)向集成系统( IS)转变的大方向下产生的。1994年Motorola发布的FlexCore系统(用来制作基于68000和PowerPC的定制微处理器)和1995年LSILogic公司为Sony公司设计的SOC,可能是基于IP( IntellectualProperty)核完成SOC设计的最早报导。由于SOC可以充分利用已有的设计积累,显著地提高了ASIC的设计能力,因此发展非常迅速,引起了工业界和学术界的关注。

SOC是集成电路发展的必然趋势,是技术发展的必然,也是IC 产业未来的发展。

本文转自:造芯师,转载此文目的在于传递更多信息,版权归原作者所有。如不支持转载,请联系小编demi@eetrend.com删除。