来源:Astroys

由于chiplet据称能够将一个庞大、先进的SoC解构为相对低端制程的较小的die,从而暗示了一种绕过摩尔定律的道路。通过提供一种替代方案,chiplet也有望改变10nm以上芯片制造的两方垄断局面,从而带来更多样化、更稳健的供应链。

Chiplet听起来似乎简单,但其背的SiP(system-in-package)技术却是一项非同小可的技术。在基于chiplet的SiP推广之前,必须克服几类技术挑战。目前的迹象是乐观的,但chiplet得到普及还有一段路要走。

KGD问题

首先是KGD(known good die)问题,这是一个乘法问题。简单来说,SiP能够正常工作的概率小于SiP中每个单独die的良率的乘积(假设这些单个概率在统计上是独立的)。

如果你有一个由两个die组成的SiP(比如,一个CPU和一个大cache),假如CPU die的良率是90%,cache的良率是98%,那么你就可以推算出SiP的良率,即两者的乘积,大约88%。

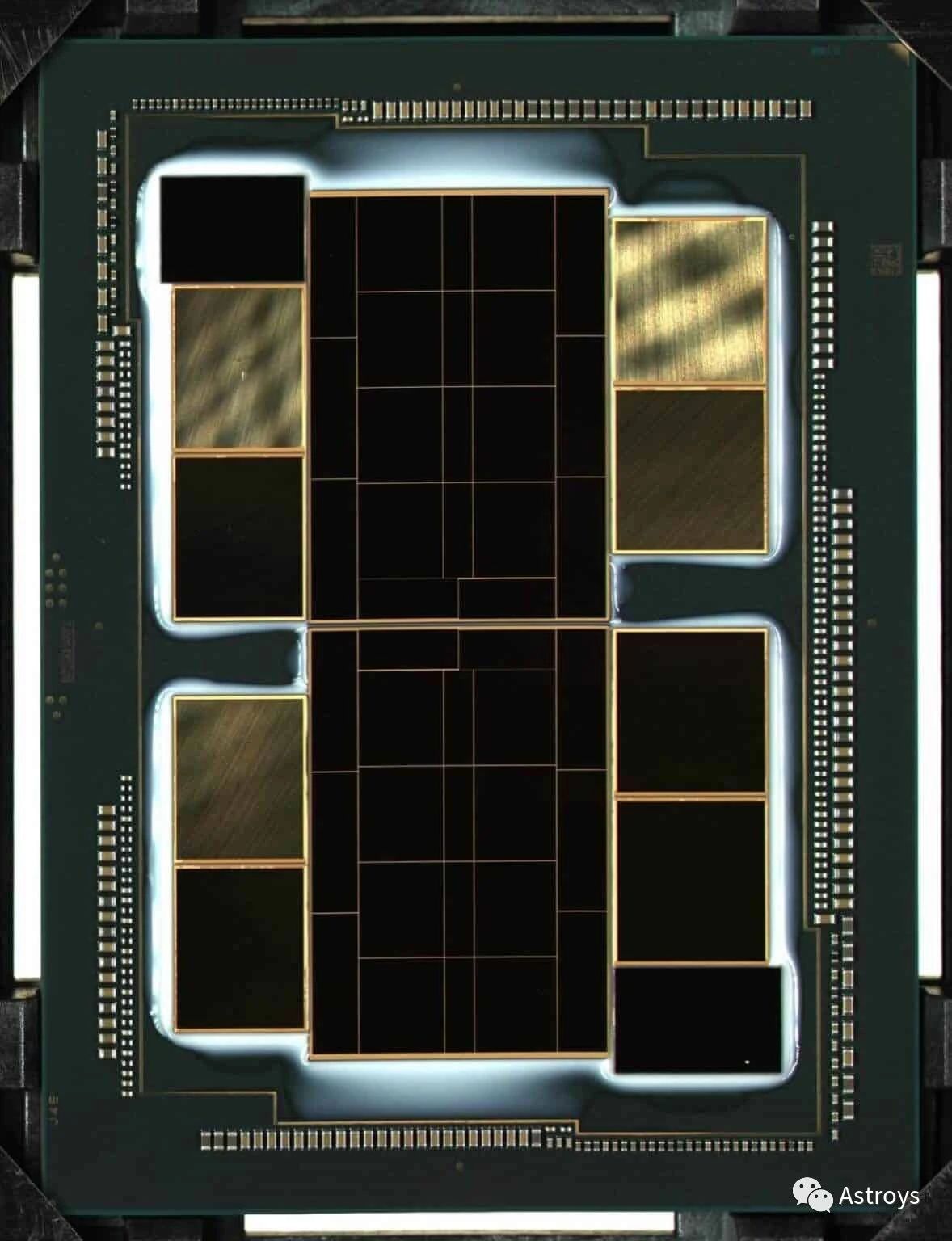

于是,这个问题很快就会变得比较复杂。例如,Intel最近宣布,其Ponte Vecchio GPU SiP包含惊人的47种不同类型的die。如果进入SiP的每个die中有1%是有问题的,即使在装配、封装和测试中没有任何损失,Intel也只能在装配和封装后获得低于63%的良率。如果这个进料异常率提高到10%,那么大约每150个GPU SiP中只有一个是可以正常工作的。

那么,该怎么做呢?显然,第一步是尽一切可能降低进料异常率。这包括在每个入厂die的测试阶段增强测试覆盖。Chiplet供应商(尤其是所有的die不是来自同一供应商的情况下)必须不仅测试短路或开路,还要测试时序故障、内存性能,以及可能暗示早期老化故障的参数,包括他们能识别出可能导致SiP提前失效的任何问题。在晶圆经过测试并分解成单独的die之后,可能需要再次通过光学检查和电气测试,以排除在分离过程中受损的die。

即使进行了广泛的测试覆盖,仍然会存在问题。测试向量不可避免地会遗漏一些故障。有些故障会是间歇性的,或者只会随时间的推移出现。在某些设计中,要达到在SiP级别上可接受的良率可能需要冗余和自我修复技术,而这些技术目前在某些特定的关键任务芯片之外还处于非常早期的开发阶段。或者,可能需要一种实际的方法来修复SiP,而不是丢弃它,这在可靠性实验室之外是不可能的。在一定程度上,修复取决于SiP的组合方式。

结构几乎决定一切

在SiP中将die组合在一起有很多种方式。Die之间传输信号的方式也有很多种。这两个问题是分开的,但却相互交织。

最简单的die的排列方式是将它们像地砖一样平放在基板上。Die可以是正面朝上,也可以是正面朝下。基板可以是用于单个die封装的同一材料,或者是更先进的有机材料,支持更细的互连线路和更精细控制的阻抗。或者,它可以是硅。在不久的将来,包括Intel在内的一些公司可能会开始使用玻璃。

如果你需要减小SiP的面积,或者如果你需要让一些die物理上接触到彼此,以便在它们之间获取更多或更快的连接,你可以将die堆叠起来。这可能意味着简单地将一个die放在其他die的上面,使边缘重叠,或者在一个更大的die上放一个更小的die。或者,它可能意味着建造精细的die塔,比如在内存控制器die上堆叠一堆高带宽内存die,形成一个非常快速的DRAM塔。这些技术的组合也是可能的。

互联问题

互连是另一个问题。如何将信号和电源从一个地方传输到另一个地方取决于很多因素:涉及信号数量、带宽或比特率、你能容忍的延迟,以及你的预算。

除了最后一点,所有这些都受到一个因素的强烈影响:系统架构如何巧妙地分割为chiplet。如果它们之间只有少数低速总线和控制信号,那么互连就很容易。相反,如果在SiP中分布的chiplet之间有数千个信号,而它们的速度限制了最终系统的性能,那么只有最先进的封装才能有效地工作。

一旦你量化了互连需求,就有很多可选方案。首先是传统的线键合,在die和基板上的键合垫之间串接超细线。线键合可追溯到晶体管时代的初期,是已经非常成熟并且普及的技术。线键合可以将die相互连接起来,也可以将die连接到基板上的键合垫上。但目前线键合能提供的密度(每平方毫米的垫数)和频率最低。由于这些原因,焊线技术通常与传统封装基板材料一起使用。

如果你需要更高的互连密度或速度,你必须将一个表面上的接触点直接连接到另一个表面上的接触点。在中等密度的情况下,通常通过在两个垫之间放一个焊球来完成。在更高密度时,你需要制造一些更复杂的结构,比如一组铜柱,来连接两个表面上的垫。(在光学显微照片中,这些铜柱阵列看起来就像一个农场或城市的天际线。)

这些技术要求两个表面面对面,完全平整,并且垫要完全对齐。这需要两个die,或者die和基板,为彼此设计或设计为一个公共的接口标准。但是在某些情况下,所有的die都不能面对面安装:例如,3个die的堆栈。因此,你将不得不以某种方式将一些信号从die的活动面移动到背面的接触垫。要做到这一点,你可以在分离后的die上制作穿过die边缘、向下并绕到背面的导线。或者,现在更常用的方法是在减薄的晶片上钻通硅孔。无论如何,晶圆都需要进行特殊的处理,以创建连接并在背面制造痕迹和着陆点,这是chiplet供应商必须要理解的事实。

这些技术通常会配合使用高性能有机基板,上面带有非常精细的互连线,也可能带有一些活动部件。在最严苛的设计中,设计师可能会选择硅而非有机材料,并使用IC晶圆制造工艺的最后步骤来在硅上创建超精细的互连线。这样的硅基板通常被称为interposer。Intel使用的一个有趣的变体,称为EMIB(embedded multidie interconnect bridge),将小块的硅植入到有机基板中。Die是朝下安装的,以便它们的接触点落在EMIB桥上,这些桥在相邻的die之间传送信号。

随着这些技术变得更加精细,成本也会翻倍,因此这项技术更有可能专属于一个大型代工厂。但最近,另一种替代方案出现在许多信号需要连接的情况下,其中一些可能具有非常高的数据速率,但没有哪个特别敏感于延迟。这种技术,由初创公司Eliyan推广,借用了来自网络和FPGA行业的高速串行接口技术。但Eliyan将接口硬件简化,以符合芯片互连的特定要求,获取的接口小,功耗低,但能够在甚至是传统基板上以每秒数十Gb的速度传输数据包。你可以将信号分解成数据包,将数据包多路复用,然后将所有数据通过单线以串行方式传输。Eliyan声称,该技术可以大大减少die之间的信号线的数量。更重要的是,由于收发器可以根据普通链路的特性进行调整,因此该技术可以缓解或消除对先进封装材料和技术的需求。

大量的分析需求

一旦你决定了SiP的形式,chiplet组装需要在许多领域进行大量分析,其中只有一部分是电气方面的。例如,你需要考虑热行为。封装中的每一个die都是一个热源,有自己的热点和冷点,其位置和温度会随着系统操作模式和工作负载的不同而改变。将die组装到先进的封装中会使它们相互加热,并在die间积聚热量,从而在三维空间中产生局部的、可能是移动的热点。这些问题区域可能导致电路故障或SiP的物理损坏。因此,基于电路功率建模的动态3D热分析是必要的。

承载SiP的电路板的热膨胀和弯曲会导致SiP组件本身产生机械应力。这种应力可能会破坏微妙的互连或使die脱层。更严重的是,die上的应力会改变其晶体管的电气行为,从而导致电路故障。因此,除了热分析外,还需要对SiP进行机械分析,考虑热膨胀、外部应力和振动。

由于die间的互连比die内部的互连长得多,且物理性质也大不相同,因此需要对其进行专门的建模,通常包括完全的电磁场建模。这是为了获取穿越die间路径的精确计时,以及进行信号和功率完整性分析。

另一点涉及到对组装和封装的SiP进行最终测试。由于芯片内罕见的未检测到的故障、机械损伤或互连故障,故障总会发生的。但是,大部分的SiP信号在设备封装后无法接触到测试器。因此,测试设计师必须达到出色的测试覆盖率(并在此基础上提供故障的根本原因分析),同时必须严重依赖chiplet本身的内建的自我测试。

这只是基于chiplet的SiP可能面临的问题的一些要点。虽然技术基本上已经到位,尽管更先进的技术如今是各个主要代工厂的专利。许多分析工具已经存在,并正在凝聚成更易于操作的平台。但是,从架构划分的基础知识到die设计,再到封装设计和分析,到供应链管理的每个方面的学习曲线都很艰难,并且每个领域经验丰富的工程师都很稀缺。今天,将chiplet从一个伟大的想法落地为一种可行的技术,再转变为一种主流选择,仍然是一个进行中的工作。

本文转自:Astroys,转载此文目的在于传递更多信息,版权归原作者所有。如不支持转载,请联系小编demi@eetrend.com删除。