2023年10月13-16日,第四届中国计算机学会集成电路设计与自动化学术会议(CCF Integrated Circuit Design and Automation Conference, CCFDAC) 集成电路年度大会在北京召开!

大会重磅发布了《集成芯片与芯粒技术白皮书》,该白皮书是由刘明院士和孙凝晖院士牵头,由集成芯片前沿技术科学基础专家组、中国计算机学会集成电路专业委员会、中国计算机学会容错计算专业委员会共同编著。

▎白皮书说明:

本白皮书基于“集成芯片前沿技术科学基础”专家组组织的多次讨论内容,由秘书组全体成员共同整理和编写而成。在编写过程中,为了更全面地呈现本领域相关技术,编写组增加了部分技术调研内容和趋势判断分析。集成芯片作为一个新兴领域,其涉及的概念和技术仍处于不断发展之中,我们也意识到本白皮书中可能存在内容阐述不够充分、不够系统的问题,也诚恳欢迎提出宝贵建议。

联系人:韩银和(中国科学院计算技术研究所),秘书组组长

邮 箱:yinhes@ict.ac.cn

▎白皮书意义:

《集成芯片与芯粒技术白皮书》(以下简称“白皮书”)阐述了集成芯片与芯粒的内涵、集成芯片架构与电路设计技术、集成芯片EDA 和多物理场仿真技术、集成芯片的工艺原理,最后介绍了集成芯片的设计挑战与机遇。

具体结构如下:

第一章,介绍了发展集成芯片和芯粒的重要意义以及本技术白皮书的内容。

第二章,概述了集成芯片与芯粒的内涵。

第三章,分析了集成芯片架构与电路设计技术,详细阐述集成芯片设计方法、多芯粒并行架构、芯粒互连接口协议以及芯粒间高速接口电路等关键技术。

第四章,分析了集成芯片EDA 和多物理场仿真的相关技术,包括集成芯片布局布线EDA、芯粒尺度的电- 热- 力多场耦合仿真以及集成芯片的可测性与测试技术。

第五章,分析了集成芯片的工艺原理,包括RDL/ 硅基板(Interposer)制造工艺、高密度凸点键合和集成工艺、基于半导体精密制造的散热工艺等。

第六章,讨论了集成芯片的设计挑战与机遇,为未来集成芯片的发展提供参考路径。

在高性能芯片发展受制的背景下,从我国的产业现状出发,发展集成芯片——这条不单纯依赖尺寸微缩的新路径,是我国集成电路领域的重要的发展方向。本白皮书希望学术界和产业界更广泛而深入地了解集成芯片和芯粒技术,共同推进集成芯片技术蓬勃发展。

▎集成芯片与芯粒

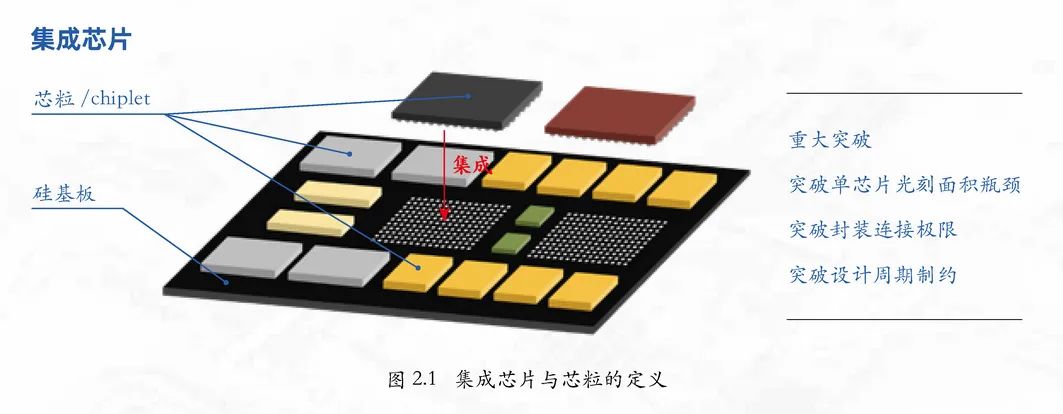

传统集成电路是通过将大量晶体管集成制造在一个硅衬底的二维平面上形成的芯片。集成芯片是指先将晶体管集成制造为特定功能的芯粒(Chiplet),再按照应用需求将芯粒通过半导体技术集成制造为芯片。其中,芯粒(Chiplet)是指预先制造好、具有特定功能、可组合集成的晶片(Die),也有称为“小芯片”,其功能可包括通用处理器、存储器、图形处理器、加密引擎、网络接口等。硅基板(Silicon Interposer),是指在集成芯片中位于芯粒和封装基板(Substrate)之间连接多个芯粒且基于硅工艺制造的载体,也有称为“硅转接板”、“中介层”。硅基板通常包含多层、高密度互连线网络、硅通孔(Through Silicon Via, TSV) 和微凸点(Micro Bump),保证了电源、数据信号在芯粒之间和封装内外的传输,而且可以集成电容、电感等无源元件和晶体管等有源电路。

▎集成芯片的现状和趋势

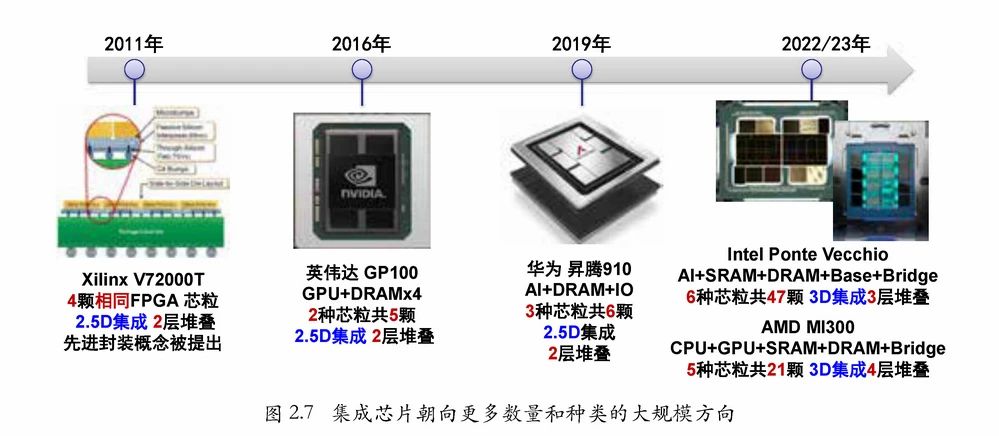

最早的集成芯片原型是由台积电与美国赛灵思(Xilinx)公司共同完成的一款大容量FPGA 芯片V7200T,它将四个大规模的FPGA 芯粒在一块硅基板(Interposer)上连接在一起,形成一个超过2000个可编程逻辑门的系统。借助这一芯片的开发,台积电也完成了基于半导体工艺的芯片互连封装技术,称为Chip-on-Wafer-on-Substrate(CoWoS)。目前这一技术作为2.5D 集成芯片的代表性工艺,广泛的应用于高性能处理器芯片产品中。第一个采用CoWoS 技术的处理器集成芯片是英伟达公司的GP100 GPU 芯片,它的结构是通过CoWoS 工艺将GPU 芯粒和多个HBM 芯粒在一个封装体内集成,最大化处理器与存储之间的通信带宽,硅基板尺寸超过1 个光罩(858 mm2)。我国华为海思公司设计的昇腾910芯片,也是基于这一技术将3 种、6 个芯粒的集成,实现了高算力的人工智能处理器。

近年来,随着TSV、铜- 铜混合键合等工艺的成熟,3D集成芯片成为了高性能处理器领域新的发展趋势。美国AMD和Intel公司均基于3D集成芯片技术,设计了面向超算的高性能超算处理器芯片。上述产品将将6-8种,超过20个芯粒的芯粒集成在一个系统中,最终实现了更大规模(千亿以上规模数量级晶体管)、更复杂的集成。在2.5D集成上,基于重分布层(Re-Distribution Layer)的扇出工艺(FanOut)可以实现更大规模的芯粒集成,美国Tesla 公司基于FanOut工艺开发面向人工智能的训练处理器集成芯片DOJO,RDL基板的总面积达到20000 mm2,包含25个D1多核处理器芯粒和光电融合的通信芯粒。

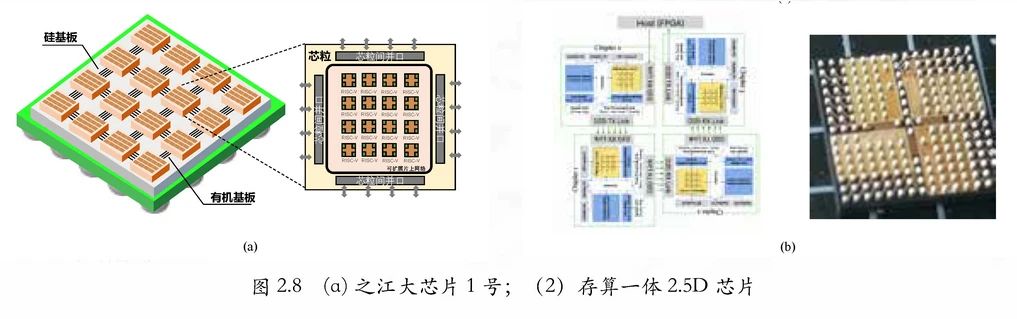

我国研发机构在高集成度上取得了进展。比较有代表性的包含,2022 年中科院计算所智能计算机中心和之江实验室联合开发了“之江大芯片一号”,该芯片成果集成了16个芯粒,每个芯粒含16个CPU核,无论是集成的芯粒数和体系结构上的计算核心数,都实现了突破,从体系架构和设计方法学上,验证了利用集成芯片突破单处理器芯片的算力极限技术途径。目前,正在开展“之江大芯片二号”的工作,集成度和性能将进一步提升。2022年,复旦大学集成芯片与系统全国重点实验室基于集成扇出封装工艺实现了存算一体2.5D芯片,采用片间按层流水的可扩展架构实现了系统算力与存储规模的按芯粒比例的线性增长,避免了“一系统一设计”的高复杂度问题。此外,阿里达摩院联合紫光国芯研发基于3D混合键合工艺的智能加速器-DRAM 堆叠集成芯片,豪威科技的采用三层堆叠工艺将图像传感器芯粒、模拟读出电路芯粒、图像信号处理与AI 芯粒集成为一个组件,面向像素的不断提升,最小化芯粒间的通信开销。

集成芯片中,由于每个芯粒由不同的单位设计,因此接口的标准化是系统能够高效率组合的关键因素。在Intel 的主导下,2022年3月,通用高速接口联盟(Universal Chiplet Interconnect Express, UCIe)正式成立,旨在构建芯粒技术在芯片上的互联标准。在我国,中国计算机互连技术联盟的《小芯片接口总线技术要求》和中关村高性能芯片互联技术联盟的《芯粒互联接口规范》等接口规范也已公布。

▎集成芯片的三大科学问题与十大技术难题

集成芯片的发展仍处于初级阶段,目前国内外的商业化集成芯片产品普遍面临集成度低的问题,如芯粒数量一般少于10个、芯粒种类少于5种,远远未能发挥该设计应有的性能优势。

我们认为:集成芯片的集成度(种类和规模)的提升,是推动集成芯片技术体系的主要驱动力量。

集成度的大幅提升,将引发从芯片设计方法学、体系结构、仿真工具到底层工艺制备等一系列的科学问题。

科学问题一:

芯粒的数学描述和组合优化理论。面向分解中的数学问题,目的是解决如何将复杂的功能需求,分解并映射到大规模的芯粒构件上。在少量芯粒集成时,映射关系较为简洁,而将复杂功能分解到大量芯粒时,则需要借助数学运算来完成和优化。传统集成电路针对微观晶体管的数学描述并不适用于芯粒尺度,因此亟需建立新的数学理论。传统集成电路设计依靠的布尔代数、符号逻辑等方法,不适用于介观尺度的芯粒功能分解。这一理论不是简单的Top-Down 的宏观系统拆分方法的迁移,需要探究应用场景下芯粒的抽象表达,为大规模集成芯片的分解提供理论基础。

科学问题二:

大规模芯粒并行架构和设计自动化。面向芯粒组合并行挑战的信息科学问题,解决随着芯粒的数量和种类大幅提升,怎样应对芯片设计复杂度的爆炸式增长问题。需要设计超越多核架构的高并行效率新架构,充分释放芯粒组合并行的算力潜能,破解阿梅达尔定律和计算- 通信屋顶曲线模型等带来的扩展性和并行极限难题。另一方面,少量芯粒集成时由于涉及的芯粒种类少、复用率低、空间维度小,现有EDA 工具主要用于以晶体管为单元的二维电路设计,无法辅助以芯粒为单元的三维布局开发。因此需要突破芯粒层面的设计语言和综合问题,探索新布局布线方法,形成集成芯片EDA 新工具,大幅降低集成芯片设计周期。

科学问题三:

芯粒尺度的热力电多场耦合机制与界面理论。面向集成挑战的物理科学问题,目的是解决不同功能和种类的芯粒在形成界面时,如何优化热、电传导,避免应力破坏等问题。大规模芯粒集成将扩展到三维空间,多层堆叠结构带来了复杂界面的物理量传导耦合问题。集成芯片需要准确预测系统在多物理场中运行状态,特别是电磁场、热和应力翘曲,并在跨尺度下形成较为完整的研究体系。然而,现有的宏观结构力学、工程热学与量子器件的微观表面力学等理论缺乏深层次耦合交互。以热仿真为例,微观层面上在器件、量子尺度的热仿真理论采用波尔茨曼输运理论等,宏观层面上在大封装尺度的热理论采用热传导、扩散方程等,在芯粒尺度的热界面理论不完善;在集成芯片须明晰多芯粒系统中的电磁、热和应力的相互作用,探索跨尺度的多物理场交互的仿真方法与工具。

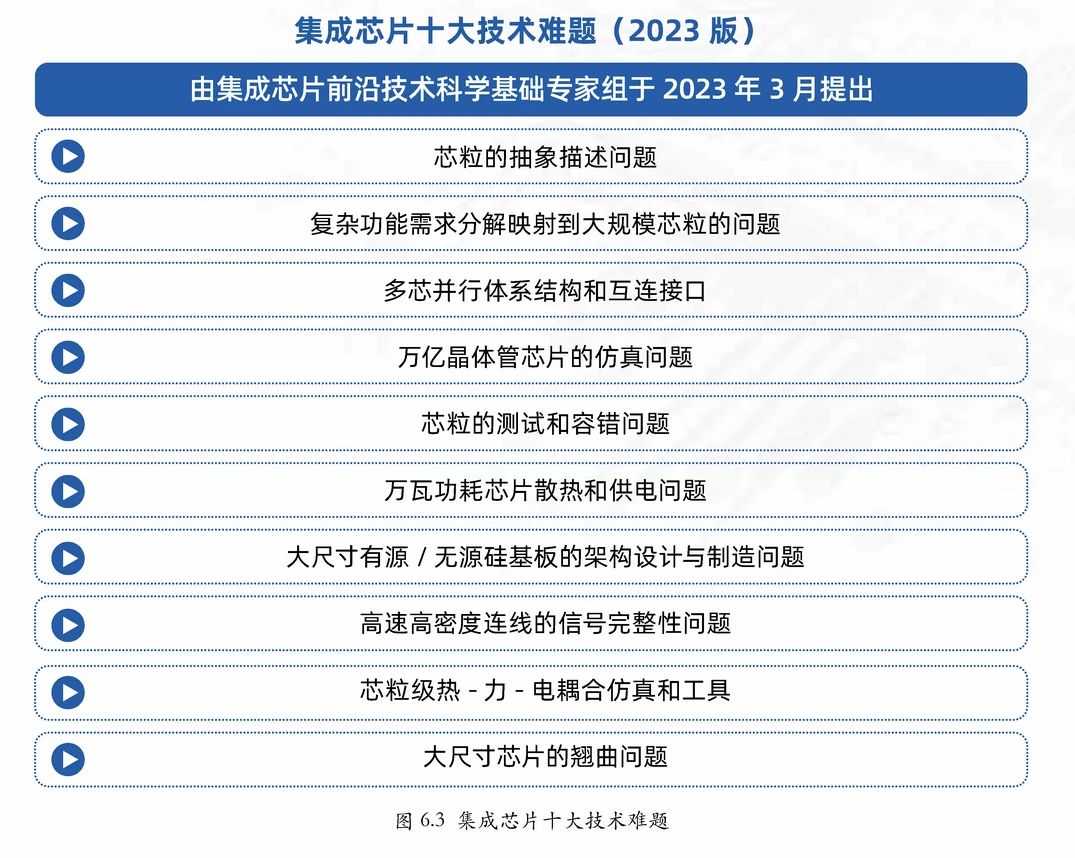

在以上集成芯片的科学问题基础上,集成芯片前沿技术科学基础专家组进一步提出十大技术难题(2023版),见下图,希望这些问题能为集成芯片的发展起到牵引作用。

本文转自: 电子与信息学报,转载此文目的在于传递更多信息,版权归原作者所有。如不支持转载,请联系小编demi@eetrend.com删除。