1、What is SoC?

SoC(System on Chip),系统级芯片(片上系统)SoC是将系统的主要功能综合到一块芯片中,本质上是做一种复杂的IC设计。SoC是集成电路设计和制造工艺发展的产物,它可以将整个系统集成在一个芯片上。

分类:

专用SoC:专用集成电路(ASIC)向系统级集成的自然发展;

通用SoC:将CPU、DSP、RAM等集成在芯片上,同时提供用户设计所需要的逻辑资源和软件编程所需要的软件资源。

在目前的集成电路设计理念中,IP是构成SoC的基本单元,IP是指由各种超级宏单元模块电路组成并经过验证的芯核,可以理解为满足特定规范,并能在设计中复用的功能模块。

从IP的角度出发,SoC可以定义为基于IP模块的复用技术,以嵌入式系统为核心,把整个系统集成在单个芯片上完成整个系统功能的复杂的集成电路。目前的SoC集成了诸如处理器、存储器、I/O端口等多种IP。

2、SoC Design challenges

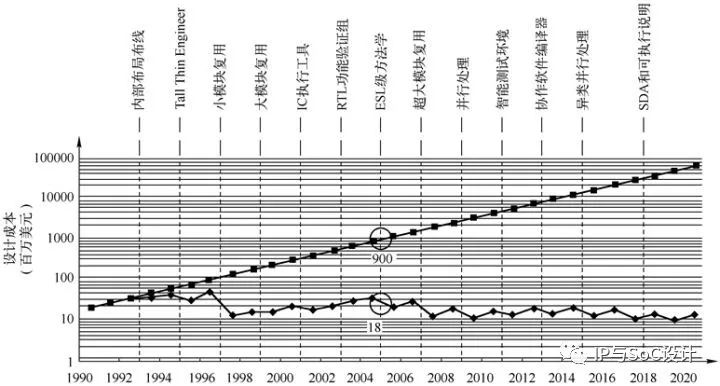

1. 设计的复杂性

设计的复杂性主要体现在芯片验证和测试难度的提高,以及IP复用、混合电路设计的困难加大。

-芯片验证更加复杂:电路规模的增加导致庞大的设计数据和更为复杂的验证过程,集成度越高,实现的功能越丰富,所需要验证过程就越繁琐,验证向量的需求也就越多。IP核的多样性造成了验证的复杂性。

-芯片测试更为复杂:集成密度的提高导致的,芯片规模的增大,导致外围引脚的增加,并且内部逻辑越来越复杂,会生成海量的测试矢量。

-混合电路设计更为复杂:数字模拟的混合电路的集成。数字部分:处理器、存储器外围接口等;模拟部分包括射频电路以及数模、模数转换电路。模拟电路的集成度远低于数字电路,要在高密度下实现数字电路和模拟电路的集成和信号交互,就必须重新考虑设计方法、设计工具、制造封装方法等因素。

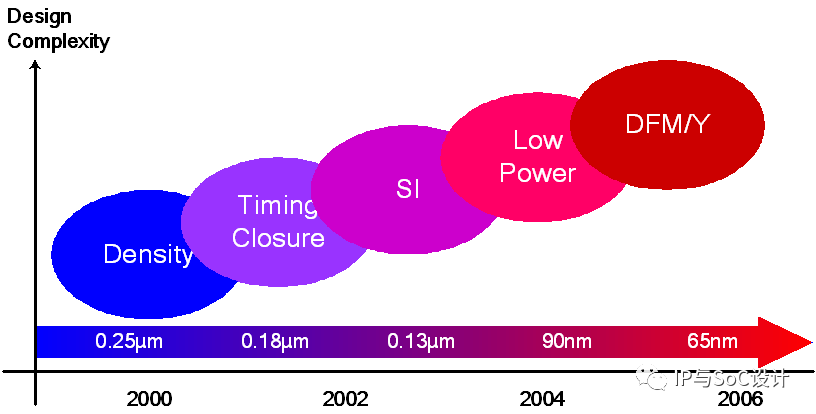

2. 时序收敛

集成电路设计中的时序收敛一般是指前后端设计时序能够达到设计需求。随着工艺的进步,线延迟占据主导地位,时序收敛问题越来越严重。设计工具的时序准确性不足以及版图后的时序收敛问题已经成为实现这类设计项目的关键障碍。60%以上的ASIC设计都存在时序收敛的问题。

3. 信号完整性

信号完整性是指一个信号在电路中产生正确的、相应的能力。信号具有良好的信号完整性是指,在需要的时间段内,该信号具有所需要达到的电压电平数值。在SoC设计中,信号之间的耦合作用会产生信号完整性问题,忽视信号完整性问题可能导致信号i之间产生串扰,可靠性,可制造性和系统性能也会降低。

4. 低功耗设计

随着IC工作频率、集成度、复杂度的不断提高,IC的功耗快速增加,功耗的增加带来了一系列的现实问题及设计挑战:

功耗增加引起的IC运行温度上升会缩短芯片寿命,并且对系统冷却的要求也相应提高,不仅增加了系统成本也限制了系统性能的进一步提高。

功耗增加引起的IC运行温度上升会引起半导体电路的运行参数漂移,降低了电路的可靠性和性能。

为了进行低功耗设计,选择不同性能参数的器件,如多阈值电压的MOS管、不同电源电压的器件等,这样一来就大大增加了设计复杂度。

5. 可制造设计(DFM)及成品率

在65nm及以下的工艺,可制造性设计尤为重要。

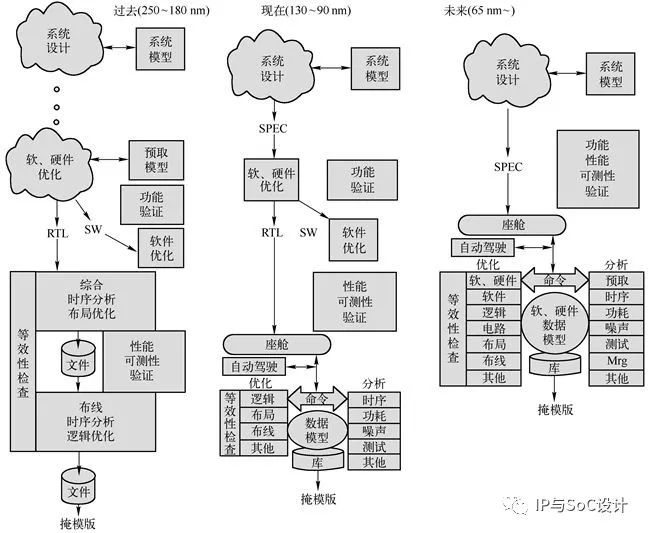

3、SoC Design Trend

随着集成电路制造工艺的发展,SoC上将集成更多数量和种类的器件。设计、制造、封装和测试变得越来越密不可分。同时,人们对高效能的SoC的需求会更加迫切。未来的SoC中将会用到更多处理器或加速器,以便更加灵活地支持不断出现的新应用。设计方法也会改进来应对新的挑战,它会对新设计工具提出新的要求,产生新的技术。

设计系统架构的发展

- IP复用将不仅仅在硬件领域,在软件设计领域同样需要;

- 今后的设计将在一个应用平台上完成,该平台将包括一个或多个处理器和逻辑单元,即基于平台的设计;

- 可编程、可配置、可扩展的处理器核的使用会使得原有的设计流程和设计者思维发生变化;

- 系统级验证时,利用高级语言搭建验证平台和编写验证向量,需要相应的工具支持;

- 软硬件协同综合,使得在同样的约束条件下,系统达到最优的设计性能。

作者:QZSL

来源:IP与SoC设计